# 100G EDR and QSFP+ Cable Test Solutions

(IBTA, 100GbE, CEI)

DesignCon 2017 James Morgante Anritsu Company

### **Presenter Bio**

James Morgante Application Engineer Eastern United States \_\_\_\_\_ james.morgante@anritsu.com

Wireline Digital / Optical Products

#### **Career Experience**

Product Development RF, Mixed-Signal & Optical, Application Engineering, Test Engineering Signal Integrity

### **Presentation Focus**

**QSFP+** Cables / Modules

Roadmap

Active Time Domain (ATD) Test Objective

EDR ATD Test System Overview

Equipment requirements

The calibration process

The DUT test

AOC final test

InfiniBand & PAM4 (200G)

# **100G Modules & AOCs**

- QSFP+ Connectors.

- 4 x 25.78125 Gb/s Electrical Interface

- Data transfers rates over 100Gb/s

- Copper and Optical.

- Single & Multimode

- Multiple Fibers (IBTA EDR, 100GBase-SR4)

- Multiple Wavelengths (IEEE 100GBase-LR4)

- Single or Multiple connections per lane of traffic.

# **IBTA Interconnects**

| InfiniBand Data    | Baud Rate<br>(Gbaud) | Per Lane<br>(Gb/s) | x4 Lanes<br>(Gb/s) | Modulation |      |

|--------------------|----------------------|--------------------|--------------------|------------|------|

| Single Data Rate   | SDR                  | 2.50               | 2.50               | 10.00      | NRZ  |

| Double Data Rate   | DDR                  | 5.00               | 5.00               | 20.00      | NRZ  |

| Quad Data Rate QDR |                      | 10.00              | 10.00              | 40.00      | NRZ  |

| Fourteen Data Rate | FDR                  | 14.06              | 14.06              | 56.24      | NRZ  |

| Enhanced Data Rate | EDR                  | 25.78              | 25.78              | 103.12     | NRZ  |

| High Data Rate     | HDR                  | 25.78              | 51.56              | 206.24     | PAM4 |

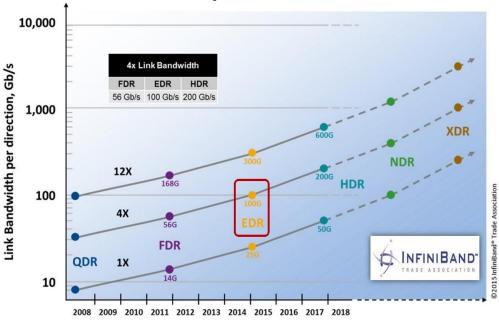

#### InfiniBand Roadmap

http://infinibandta.org/content/pages.php?pg=technology\_overview

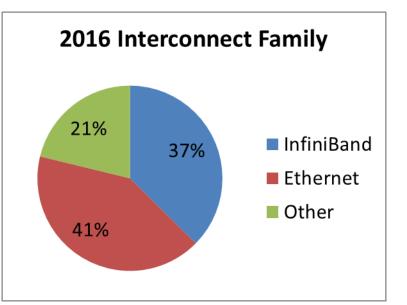

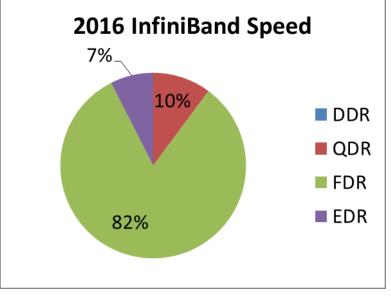

http://www.top500.org/lists/2016/11/

### **ATD (Stressed Receiver) Test Objective**

- Live Demo @ Anritsu Booth # 633

- Stressed receiver sensitivity

- Output eye compliance

- Fully described in EDR MOI: https://cw.infinibandta.org/document/dl/7807

- Test methods used at IBTA Plugfests for EDR AOCs

- **Simplified** test approach.

- 4-Lane BER, 1-Lane Time Domain

#### InfiniBand Trade Association

Anritsu / Keysight Method Of Implementation

Active Time Domain Testing For EDR Active Cables

# InfiniBand ATD Advancement

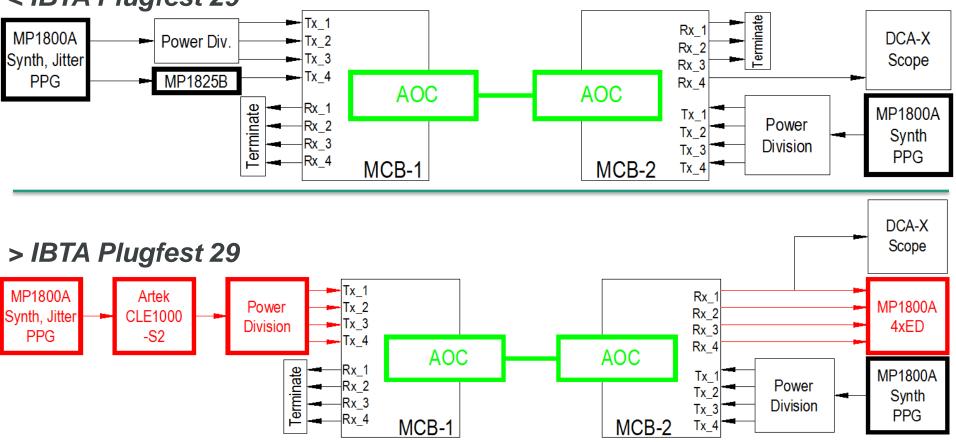

#### < IBTA Plugfest 29

#### Changes:

- Adopted CAUI-4 Stressed Signal calibration methods described in 802.3bm Annex 83E.

- Calibration through a channel and usage of DCA-X CTLE function to emulate DUT CTLE.

- BER measurements to judge performance of DUT under stressed conditions.

- DUT CTLE to compensate for channel loss during test.

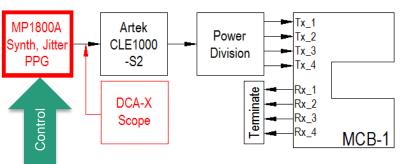

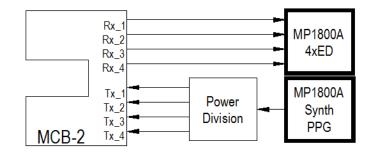

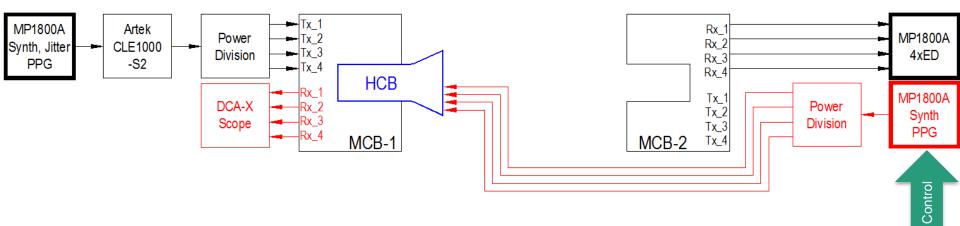

# **Principal Components**

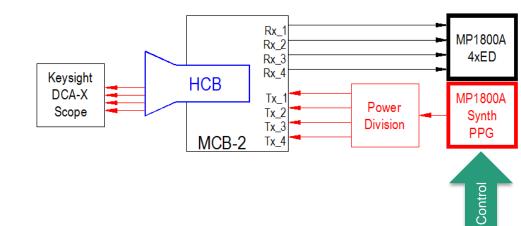

Multi-Port BERT Anritsu MP1800A Shown

High BW Sampling Scope Keysight DCA-X Shown

Compliance Fixtures Wilder Technologies MCB /HCB

| Softw                                                                                                                                                                                                                                                                                                                      | are Forge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stopped                                                                                                                                                                                                                                                                                                                    | Stopped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Rx Ampl. Range     Temp.       0     1     2       0     1     2       Tx CR     Rx CR     1       1     2     3       Tx CTLE Setting     1     2       0     1     2       4     5     6       7     Tx Fault       1     2     3       4     5     6       7     Tx Fault       1     2     3       A     7       Reset | Rx Ampl. Range       Temp.         0       1       2       0.0000 °C         Clock Recovery       Rx LOS       1       2       3       4         Tx CR       Rx CR       1       2       3       4         Rx CDR LOL       1       2       3       4         Alarm       Reset       v       v       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <td< th=""></td<> |

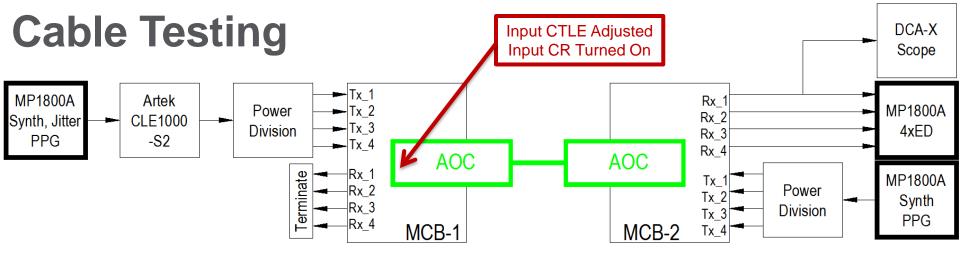

AOC Control Software Forge EEPROM Command Center

Variable ISI Channel Artek CLE-1000-S2

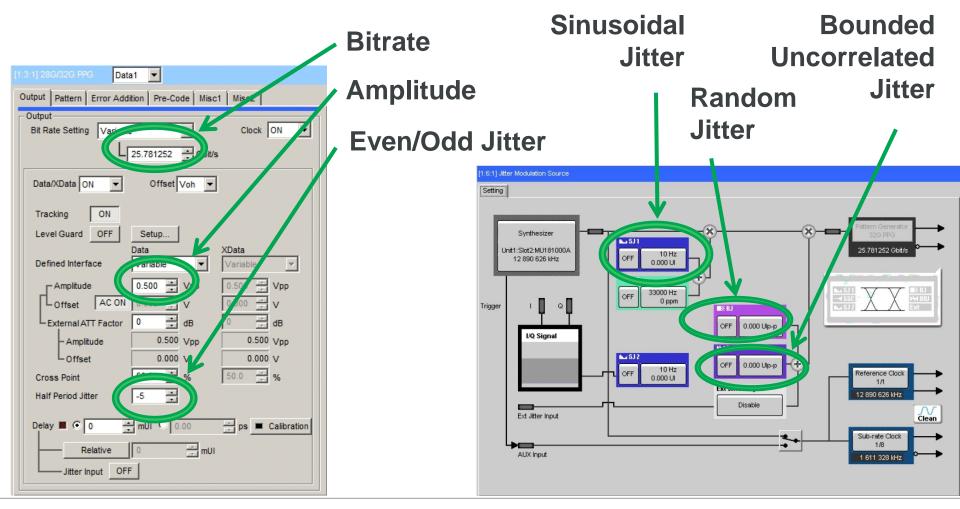

### Pattern Generators (Anritsu MP1800A SQA)

- Generating the right Stress Recipe

- Multi-Channel for Forward & Reverse Traffic

- Comprehensive control of signal characteristics & applied jitter

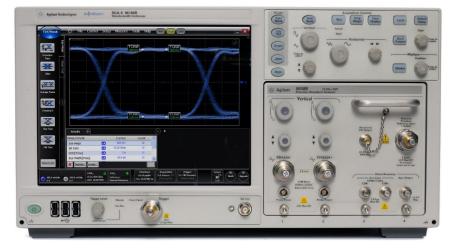

# Measurement Equipment (DCA-X 86100D, MP1800A SQA)

#### Scope: (DCA-X 86100D / 86108B)

- For Victim Input Signal Cal & DUT Measurements

- 2-Channel input for differential measurements

- ≈ 50 GHz Bandwidth

- Jitter Decomposition & Analysis Software

- o DDPWS, J2, J9 Jitter

- Eye Mask Compliance testing

- Victim Input & Victim Output

- Precision Time Base

- Clock Recovery Capabilities

- o 1<sup>st</sup> order, LBW 10MHz,

- o 0 dB peaking, 20dB/decade roll/off

- CTLE needed for calibration

#### Error Detector: (MP1800A / MU183040B)

- Used for DUT Measurements

- Multi-Channel to monitor all lanes.

- Measure BER

| 12 File                        | 1          |                                |        |  |  |  |  |

|--------------------------------|------------|--------------------------------|--------|--|--|--|--|

| 1:3:1 MU1830408 Data1 ER Total | 1.34976-07 | 1:3:1 MU183040B Data1 EC Total | 417578 |  |  |  |  |

| 1:3:1 MU183040B Data2 ER Total | 4.6300E-08 | 1:3:1 MU1830408 Data2 EC Total | 143241 |  |  |  |  |

| 1:4:1 MU183040B Data1 ER Total | 1.6161E-12 | 1:4:1 MU183040B Data1 EC Total | 5      |  |  |  |  |

| 1:4:1 MU1830408 Data2 ER Total | 1.4260E-08 | 1:4:1 MU183040B Date2 EC Total | 44119  |  |  |  |  |

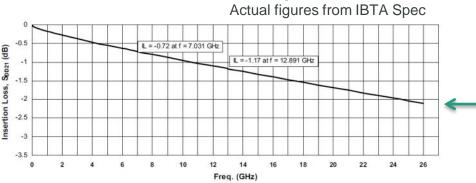

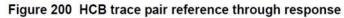

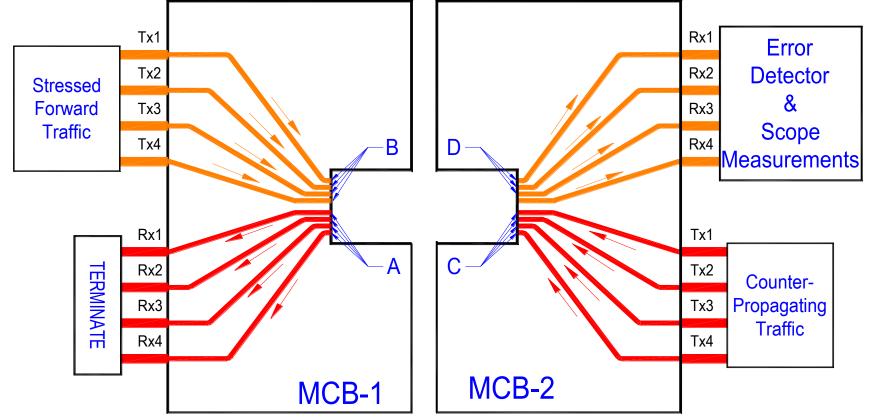

### Test Fixtures (Wilder Technologies)

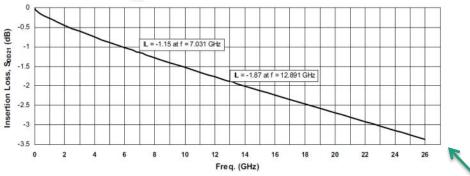

Figure 201 MCB trace pair reference through response

Figure 202 Mated HCB/MCB trace pair through response

Module Compliance Boards (MCB)

- Interface between QSFP cables and test

equipment

- Drive transmit data into TX ports

- Measure received data from RX ports

- Supply power to the cable ends

- Low Speed interconnects

- Cable programming

- Reading registers

#### Host Compliance Board (HCB)

Break-out fixture to access QSFP ports

- Used only during ATD station calibration

- Inject signals into specific test points

- Measure signals at specific test points

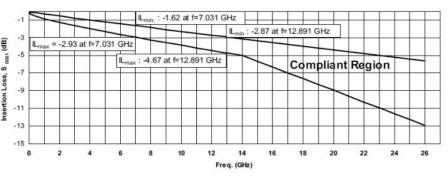

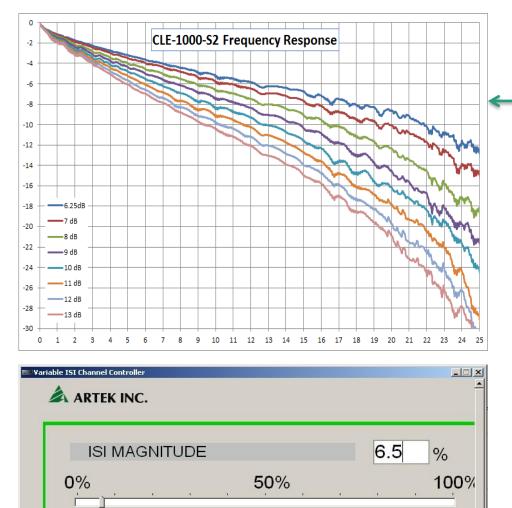

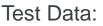

### ISI Channel (CLE-1000-S2 Ace Unitech / Artek)

#### Plugfest Data

- Objective: Create Eye Closure normally produced by channel.

- Calibration requires a specified channel loss prior to DUT

- Affected signal at output of ISI channel is divided across the 4 forward lanes.

- DUT input signal is calibrated at output of channel (-10dB @ Nyquist) using Sampling Scope & CTLE to compensate.

#### Simple control panel

Com port no

Close

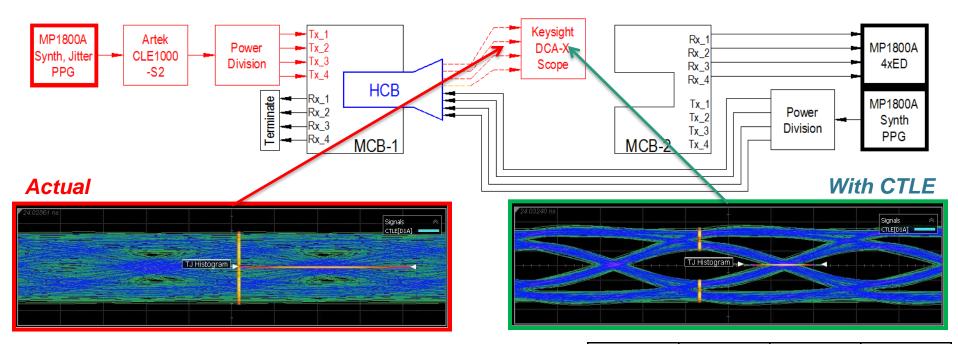

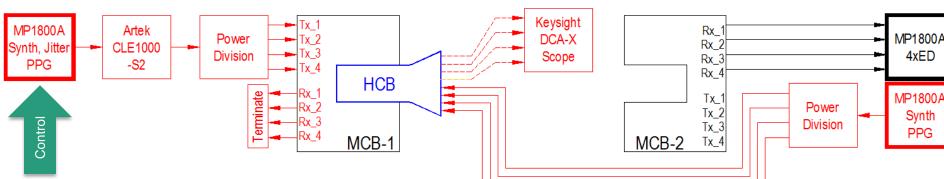

## The EDR Calibration Process Setting up equipment signals

- 1. Set PPG Source Baseline Stresses (Forward Traffic)

- 2. Set MCB-1 counter-propagating aggressors (A) for crosstalk during forward traffic calibration.

- 3. Determine & set scope CTLE.

#### 4. Set MCB-1 forward traffic (B) in presence of counter-prop aggressors.

- 5. Set MCB-2 aggressors (C) for crosstalk needed during DUT test.

- 6. Signal levels at point (D) are set after inserting DUT.

# Calibration Step 1: Setting Baseline PPG Stress

- Set baseline Even-Odd Jitter, SJ, RJ, and BUJ as required by 802.3bm, Annex 83.

- SJ characteristics

- AOC Clock Recovery stressor

- .05UI @ 91MHz (used at PF29, 30)

- Backfill with BUJ to meet TJ requirement.

- Use DCA-X Scope to verify jitter components.

#### Excerpt: 802.3bm

Table 83E–9—Pattern generator jitter characteristics

| Parameter                                | Value    |  |  |  |  |

|------------------------------------------|----------|--|--|--|--|

| Total Jitter (pk-pk) <sup>a</sup>        | 0.28 UI  |  |  |  |  |

| Random Jitter (pk-pk) <sup>b</sup>       | 0.15 UI  |  |  |  |  |

| Max even-odd jitter (pk-pk) <sup>c</sup> | 0.035 UI |  |  |  |  |

<sup>a</sup>Total Jitter at BER of 10<sup>-15</sup> <sup>b</sup>Random Jitter at BER of 10<sup>-15</sup> <sup>c</sup>As defined in 92.8.3.8.1

|                           | Time                    |                                                   |                                             |                         |                    |                                                                                                  |                                                                  |                                                                                                      |                                                             |

|---------------------------|-------------------------|---------------------------------------------------|---------------------------------------------|-------------------------|--------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| RJ/PJ<br>Histogram        | Amp                     | 24.03391 ns                                       |                                             |                         |                    |                                                                                                  |                                                                  | Signals<br>Differential 1A                                                                           | *                                                           |

| DDJ Histogram             | Amplitude               |                                                   |                                             |                         |                    | TJ Histogra                                                                                      | n <b>-</b>                                                       |                                                                                                      |                                                             |

| TJ Histogram              | Meas                    |                                                   | T                                           |                         | Manager and a      |                                                                                                  |                                                                  |                                                                                                      |                                                             |

| 41 M                      | $\overline{\mathbb{C}}$ |                                                   |                                             |                         |                    |                                                                                                  |                                                                  |                                                                                                      |                                                             |

| DDJ Vs Bit                | R I                     | Jitter 🕞                                          | )                                           |                         |                    | ♥ +                                                                                              | ſ                                                                | Graphs                                                                                               | Amplit                                                      |

|                           |                         |                                                   | 781220 Gb/s Pat                             | Length: 511             |                    | Src: D1A Rate: 25.78                                                                             | 220 Gb/s Pat                                                     |                                                                                                      |                                                             |

|                           | VCR                     | Ziella en     |                                             |                         |                    |                                                                                                  |                                                                  |                                                                                                      |                                                             |

|                           | JSA/CRE                 | F/2 (p-p):                                        | 2.2 mUI                                     | TJ (1.0E-15):           | 292 mUI            | Eye Opening:                                                                                     |                                                                  | Signal Amplitude:                                                                                    |                                                             |

|                           | VCRE                    | F/2 (p-p):<br>DJ (δ - δ):                         | 2.2 mUI<br>142 mUI                          | RJ (rms):               | 9.65 mUI           | TI (1.0E-15) Ones:                                                                               | 144.0 mV                                                         | TI (1.0E-15) Zeros                                                                                   |                                                             |

| Composite TJ<br>Histogram | VCRE                    | F/2 (p-p):<br>DJ (δ - δ):<br>BUJ (δ - δ):         | 2.2 mUl<br>142 mUl<br>117.0 mUl             | RJ (rms):<br>DDJ (p-p): | 9.65 mUI<br>34 mUI | TI (1.0E-15) Ones:<br>RN (rms) Ones:                                                             | 144.0 mV<br>1.30 mV                                              | TI (1.0E-15) Zeros<br>RN (rms) Zeros:                                                                | s: 174.5 mV<br>1.400 mV                                     |

|                           | VCRE                    | F/2 (p-p):<br>DJ (δ - δ):<br>BUJ (δ - δ):<br>DCD: | 2.2 mUI<br>142 mUI<br>117.0 mUI<br>10.2 mUI | RJ (rms):               | 9.65 mUI           | TI (1.0E-15) Ones:<br>RN (rms) Ones:<br>DI (δ - δ) Ones:                                         | 144.0 mV<br>1.30 mV<br>123.5 mV                                  | TI (1.0E-15) Zeros<br>RN (rms) Zeros:<br>DI (δ - δ) Zeros:                                           | 174.5 mV<br>1.400 mV<br>152.80 mV                           |

| Histogram                 | VCRE                    | F/2 (p-p):<br>DJ (δ - δ):<br>BUJ (δ - δ):         | 2.2 mUl<br>142 mUl<br>117.0 mUl             | RJ (rms):<br>DDJ (p-p): | 9.65 mUI<br>34 mUI | TI (1.0E-15) Ones:<br>RN (rms) Ones:<br>DI (δ - δ) Ones:<br>ISI (p-p) Ones:                      | 144.0 mV<br>1.30 mV<br>123.5 mV<br>125.30 mV                     | TI (1.0E-15) Zeros<br>RN (rms) Zeros:<br>DI (δ - δ) Zeros:<br>ISI (p-p) Zeros:                       | 174.5 mV<br>1.400 mV<br>152.80 mV<br>155.55 mV              |

| Histogram                 | VCRE                    | F/2 (p-p):<br>DJ (δ - δ):<br>BUJ (δ - δ):<br>DCD: | 2.2 mUI<br>142 mUI<br>117.0 mUI<br>10.2 mUI | RJ (rms):<br>DDJ (p-p): | 9.65 mUI<br>34 mUI | TI (1.0E-15) Ones:<br>RN (rms) Ones:<br>DI (δ - δ) Ones:<br>ISI (p-p) Ones:<br>BUI (δ - δ) Ones: | 144.0 mV<br>1.30 mV<br>123.5 mV<br>125.30 mV<br>1.2 mV           | TI (1.0E-15) Zeros<br>RN (rms) Zeros:<br>DI (δ - δ) Zeros:<br>ISI (p-p) Zeros:<br>BUI (δ - δ) Zeros: | 5: 174.5 mV<br>1.400 mV<br>152.80 mV<br>155.55 mV<br>460 μV |

| Composite DDJ             | VCRE                    | F/2 (p-p):<br>DJ (δ - δ):<br>BUJ (δ - δ):<br>DCD: | 2.2 mUI<br>142 mUI<br>117.0 mUI<br>10.2 mUI | RJ (rms):<br>DDJ (p-p): | 9.65 mUI<br>34 mUI | TI (1.0E-15) Ones:<br>RN (rms) Ones:<br>DI (δ - δ) Ones:<br>ISI (p-p) Ones:                      | 144.0 mV<br>1.30 mV<br>123.5 mV<br>125.30 mV<br>1.2 mV<br>600 µV | TI (1.0E-15) Zeros<br>RN (rms) Zeros:<br>DI (δ - δ) Zeros:<br>ISI (p-p) Zeros:                       | 174.5 mV<br>1.400 mV<br>152.80 mV<br>155.55 mV              |

#### Excerpt: 802.3bm 83E.3.4.1.1 Module stressed input test procedure

be below the upper frequency limit of the pattern generator external modulator input. <u>Random jitter and</u> bounded uncorrelated jitter are added such that the output of the pattern generator approximates a jitter profile given in Table 83E–9. The target pattern generator 20% to 80% transition time in the module stressed

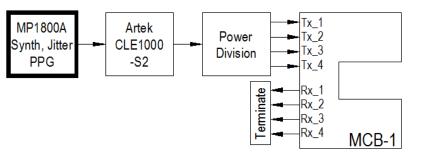

## Calibration Step 2: Setting Counter-Propagating FEXT Aggressors

- Set counter-propagating aggressor signal levels to generate crosstalk for the forward traffic calibration.

- Inject aggressors into HCB Rx ports and measure with scope at corresponding MCB-1 Rx ports.

#### Excerpt: IBTA Spec v2r1\_3\_1.160825

Table 87 EDR limiting active cable input electrical specifications

| Symbol | Parameter                                              | Specification value(s)  | Unit | Conditions                                                                                            |  |  |  |

|--------|--------------------------------------------------------|-------------------------|------|-------------------------------------------------------------------------------------------------------|--|--|--|

|        | Crosstalk signal Vpk-pk                                | +/- 5% (See Conditions) | mV   | At TP6a.                                                                                              |  |  |  |

|        | Crosstalk signal transition time, 20%-80%              | 17                      | ps   | Co-propagating aggressors.<br>Crosstalk signal Vpk-pk to match<br>lane under test, to within +/- 20%. |  |  |  |

|        | Crosstalk calibration signal<br>Vpk-pk, each aggressor | 450 +/- 10%             | m∨   | At TP7a.<br>Counter-propagating aggressors.                                                           |  |  |  |

|        | Crosstalk calibration signal transition time, 20%-80%  | 17 +/- 3                | ps   | Apply during crosstalk calibration only <sup>a</sup>                                                  |  |  |  |

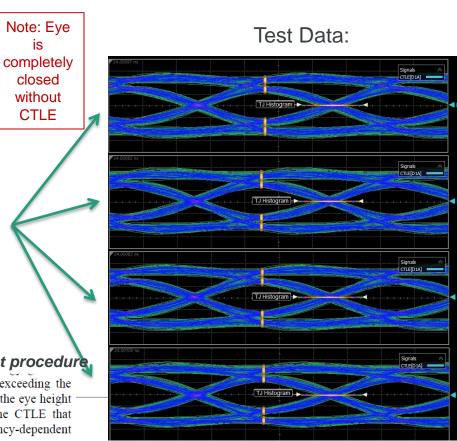

# Calibration Step 3: Determine Scope CTLE Setting

- ISI Channel will significantly close the input eye.

- Goal: Use the scope's software CTLE to simulate the effect of the DUT's hardware CTLE.

- Target Eye Width and Height must be adjusted while applying software CTLE.

- The Optimal setting = setting with maximum product.

| Scope CTLE | Eye Width<br>(UI) | Eye Height<br>(mV) | Product |

|------------|-------------------|--------------------|---------|

| 2          | 2 N/A             |                    | N/A     |

| 3          | N/A               | N/A                | N/A     |

| 4          | 0.418             | 70                 | 29.26   |

| 5          | 0.512             | 86                 | 44.03   |

| 6          | 0.536             | 102                | 54.67   |

| 7          | 0.54              | 111                | 59.94   |

| 8          | 0.512             | 114                | 58.37   |

| 9          | 0.51              | 100                | 51.00   |

# Calibration Step 4: Setting Forward Traffic Stress

is

- Send forward signal through ISI Channel & Divider.

- Counter- propagating aggressors turned on.

- Adjust the stressed forward signals.

- Adjust RJ to achieve Eye Width •

- Adjust Amplitude to achieve Eye Height ۰

- Set Eye Width & Eye Height targets per IBTA Spec

- Scope Measurement with CTLE, all channels

#### Excerpt: IBTA Spec v2r1\_3\_1.160825

| EH15 | Eye Height tolerance, at 1E-15 | 120  | mV |                                                |

|------|--------------------------------|------|----|------------------------------------------------|

| EW15 |                                | 0.53 | UI | At TP6a, with TX CDR enabled                   |

|      | Eye Width tolerance, at 1E-15  | 0.71 | UI | At TP6a, with TX CDR bypassed (i.e., disabled) |

#### Excerpt: 802.3bm 83E.3.4.1.1 Module stressed input test procedure.

83E.4.2. Random jitter and the pattern generator output amplitude are adjusted (without exceeding the differential pk-pk input voltage tolerance specification as shown in Table 83E-7) to result in the eye height and eve width given in Table 83E-8 using the reference receiver with the setting of the CTLE that maximizes the product of eye height and eye width. For the low loss case, discrete frequency-dependent

# Calibration Step 5: Setting Counter-Propagating NEXT Aggressors

- Set correct counter-propagating aggressor signal levels to generate crosstalk for the DUT Test.

- <u>Inject</u> counter–propagating aggressor signals into MCB-2 Tx ports and <u>measure</u> with scope at corresponding HCB Tx ports.

Table 88 EDR limiting active cable output electrical specifications

| Symbol | Parameter                                                                                       | Specification value(s)          | Unit | Conditions                                                                                                                                                                                |  |  |

|--------|-------------------------------------------------------------------------------------------------|---------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Х      | eye mask parameter, time;<br>see <u>Figure 86 on page 282</u>                                   | 0.30                            | UI   | Hit ratio=5E-5 with<br>100 Ohm load at TP7a                                                                                                                                               |  |  |

| Y1, Y2 | Diff. unsigned output voltage<br>range 0 (required)<br>range 1 (optional)<br>range 2 (optional) | 50, 225<br>100, 350<br>150, 450 | m∨   | (Note <sup>a</sup> )<br>At TP6a.<br>Counter-propagating aggres-<br>sors. <sup>b</sup><br>Transition time measured at<br>this PRBS9 test pattern tran-<br>sition: 1111111 <u>10</u> 000011 |  |  |

|        | Crosstalk signal Vpk-pk, each aggres-<br>sor                                                    | 700 +/- 10%                     | m∨   |                                                                                                                                                                                           |  |  |

|        | Crosstalk signal transition time,<br>20%-80%                                                    | 17 +/- 3                        | ps   |                                                                                                                                                                                           |  |  |

#### BER Measurement:

Error Free, 2 minute gate, 4 channels

Scope Measurement: J2, J9, Mask, Rise & Fall Times, 1 channel, 1M Samples

| ,                              | <b>J (</b> |                                |                     | ,                                           |                                                                                            |                                        |                                                  | ,                   |                                                                                                 |                                        |                                                |

|--------------------------------|------------|--------------------------------|---------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------|

| User Customize Dialog          |            |                                | X                   | Eye/Mask                                    | ᠰ кеүзіднт File                                                                            | e Setup M                              | leasure Tool                                     | ls Apps H           | Help                                                                                            | Auto<br>Scale                          | Run Single Clear                               |

| 12 <b>T</b> ile                |            | <b>3.</b> 14 弊 8. 11           | t 🛐 ጰ 🛓 🔜 🕨 📕 Close | - I I                                       | Waveform                                                                                   |                                        |                                                  |                     |                                                                                                 |                                        | <ul> <li>Limit (Samples) : 2000896</li> </ul>  |

| 1:3:1 MU183040B Data1 ER Total | 1.3497E-07 | 1:3:1 MU183040B Data1 EC Total | 417578              | Advanced Eye<br>Setup<br>Add Eye<br>Contour |                                                                                            | 2                                      |                                                  |                     |                                                                                                 |                                        | Signals<br>Differential IA                     |

| 1:3:1 MU183040B Data2 ER Total | 4.6300E-08 | 1:3:1 MU183040B Data2 EC Total | 143241              |                                             | P Results                                                                                  | 3                                      |                                                  |                     |                                                                                                 |                                        | Mask Test                                      |

| 1:4:1 MU183040B Data1 ER Total | 1.6161E-12 | 1:4:1 MU183040B Data1 EC Total | 5                   | RJ (ms)                                     | Measurement<br>J9 (R]: 674fs)<br>J2 (R]: 674fs)<br>J2<br>J2<br>J9<br>Eye Ampl<br>Rise Time | AIG<br>AIG<br>AIG<br>AIG<br>AIG<br>AIG | 686.8 mUI<br>471.4 mUI<br>471.4 mUI<br>849.0 mUI |                     | Max Mask 1<br>705 Source<br>489 Align Method<br>489 Waveform<br>540 Samples/U<br>Margi<br>312 + | Data Rate: 2                           | EDR_Cab_Out Change                             |

| 1:4:1 MU183040B Data2 ER Total | 1.4260E-08 | 1:4:1 MU183040B Data2 EC Total | 44119               | More (1/2)                                  | Fall Time<br>Eye Height[Ampl]                                                              | D1A<br>D1A                             | 12.66 ps                                         | 4.22 ps<br>195.8 mV |                                                                                                 | Acquisition F.<br>Full Pattern: Off Sr | Frame Trigger<br>Sec OR (Sot.1)<br>Clock/Dwded |

Scope judges Signal Integrity performance (Cable Output). ED judges BER (Cable Input).

# Cable Control EEPROM Command Center

- Developed by Software Forge for AOC management.

- Visual interface shows control and alarm activity.

- DUT features such as CTLE and CDR must be exercised to maximize chances of correct bit decisions.

- TX Clock & Data recovery at DUT Tx input reduces impact of jitter stresses applied by MP1800A Pattern Generators (likely to impact BER)

- Hardware CTLE compensates for frequency response of ISI channel, maximizing the chances of making correct bit decision. (likely to impact BER)

- Rx Clock & Data recovery further reduces waveform at far side of cable. (less likely to impact BER)

Adjust controls at cable input to optimize BER Adjust controls at cable output to optimize signal quality.

# **IBTA EDR ATD System Implementation**

#### Visit Anritsu Booth 633 for Live Demonstration

# Path to InfiniBand HDR (200G PAM4)

Considerations for ATD / Stressed Receiver Testing:

- Signal Generation / requirements / patterns used.

- **BER Measurements**

Please attend Anritsu Session for more info Toward 400G (IEEE802.3 and CEI) 56G PAM4 Bit Error Rate Test Solution 2:50 pm in Great America 2

44

# Path to InfiniBand HDR (200G PAM4)

Considerations for ATD / Stressed Receiver Testing:

- Signal Generation / requirements / patterns used.

- **BER Measurements**

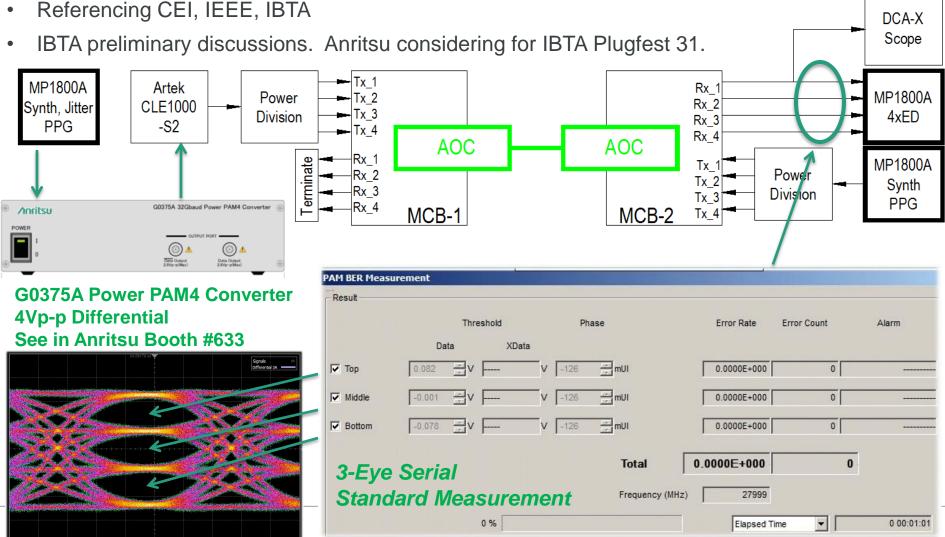

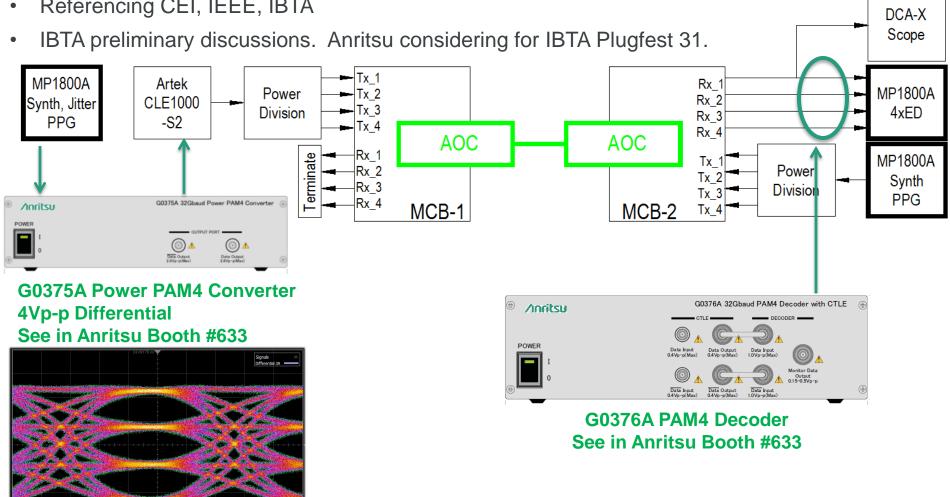

- Referencing CEI, IEEE, IBTA

Please attend Anritsu Session for more info Toward 400G (IEEE802.3 and CEI) 56G PAM4 Bit Error Rate Test Solution 2:50 pm in Great America 2

# Wrap-Up

- For Cable/Module testing, much of the time & effort goes toward achieving a spec-compliant and calibrated test station.

- Accurate & repeatable calibration means trustworthy results.

- It is important for test equipment to provide reliable control and measurement of key signal parameters.

- High-performance / quality signals and components are required so external impairments do not influence DUT results.

- The solutions presented here satisfies these requirements with proven and robust test platforms that meet the industry's growing needs.

# Thank You.

Visit Anritsu Booth 633 for Live Demonstration

# Questions?